[퀄리타스반도체]

1. 주가 흐름

2. 기업 개요

[주요 사업]

▶ 초고속 인터페이스 IP 라이선싱 : 반도체 칩 내부의 고속 데이터 전송을 담당하는 인터페이스 IP(PHY, 컨트롤러)를 설계하여 글로벌 SoC 개발사 및 디자인하우스에 라이선싱합니다. PCIe, UCIe, MIPI, eDP 등 국제표준 인터페이스 IP를 보유하고 있습니다.

▶ IP 디자인 서비스 : 고객사의 SoC(System on Chip) 개발을 지원하는 설계 서비스를 제공합니다. 고객의 요구에 맞춰 인터페이스 회로를 설계하고, 설계도면·사용설명서·동작 특성 검증 결과 등을 포함한 지식재산권을 납품합니다.

▶ 칩렛(Chiplet) 인터페이스 솔루션 : 차세대 반도체 아키텍처인 칩렛 간 고속 통신을 위한 UCIe(Universal Chiplet Interconnect Express) 표준 IP를 국내 최초로 개발하여, AI 가속기·데이터센터용 SoC 시장에 공급하고 있습니다.

[기업 기본 정보]

▶ 기업명 : (주)퀄리타스반도체 (QUALITAS SEMICONDUCTOR CO., LTD.)

▶ 상장 구분 : 코스닥 (KOSDAQ, 종목코드 432720)

▶ 설립일 : 2017년 02월 01일

▶ 회사 소재지 : 경기도 성남시 분당구 성남대로331번길 8, 609호

▶ 직원수 : 약 142명 (2024년 12월 기준)

▶ 대표자 : 김두호

[최근 시장 관심 이유]

▶ UCIe 2.0 IP 국내 최초 개발 성공 : 2025년 6월, 칩렛 간 초고속 통신 표준인 UCIe 2.0 규격 PHY IP를 국내 최초로 개발 완료하여 실리콘 검증까지 마쳤습니다. 글로벌로도 케이던스, 시놉시스, 알파웨이브 등 극소수 기업만 달성한 성과로, AI 반도체 시대 칩렛 인터페이스 IP 공급사 반열에 합류했습니다.

▶ 미국 AI 스타트업과 UCIe·PCIe 번들 첫 계약 : 2025년 하반기, 미국 AI 반도체 스타트업과 약 30억원 규모의 4nm UCIe PHY·컨트롤러 및 PCIe Gen 6.0 PHY IP 공급 계약을 체결하며, UCIe IP의 첫 번째 상업적 라이선싱을 달성했습니다. PCIe와 UCIe를 동시 공급 가능한 국내 유일의 IP 기업입니다.

▶ 중국·글로벌 고객사 확대 : 중화권 SoC 업체에 디스플레이용 MIPI IP를, 중국 팹리스에 11억원 규모 PCIe PHY IP를 공급하는 등 해외 매출이 본격화되고 있습니다. 삼성전자 파운드리 4~8nm 공정 기반 IP 포트폴리오를 확보하여 미국·중국 시장 공략을 가속하고 있습니다.

3. 주요 연혁

| 일 자 | 내 용 |

| 2017.02 | (주)퀄리타스반도체 설립 (경기도 성남시) |

| 2019.01 | 삼성전자 파운드리 SAFE IP 파트너 인증 획득 |

| 2020.01 | MIPI CSI-2 / DSI-2 PHY IP 양산 공급 개시 |

| 2020.11 | 시리즈 A 투자유치 (신용보증기금, 위벤처스 등) |

| 2021.06 | 디스플레이 인터페이스(eDP, TCON) IP 포트폴리오 확대 |

| 2022.06 | 직무발명보상 우수기업 인증, 고용노동부 강소기업 인증 |

| 2022.11 | 벤처창업진흥 유공포상 대통령 표창 수상 |

| 2022.12 | 국내 최초 100G급 SerDes 생산기술 확보 (세계 7번째) |

| 2023.06 | 과기정통부 'AI반도체 데이터센터 인프라 R&D' 및 '칩렛 기반 AI반도체 기술개발' 사업 선정 |

| 2023.10 | 코스닥시장 기술성장기업 특례상장 (공모가 15,000원, 공모자금 약 300억원) |

| 2024.05 | 595억원 규모 유상증자 결의 (UCIe·PCIe IP 개발 투자) |

| 2024.07 | 5나노 칩렛 UCIe PHY IP 시제품 제조 착수 |

| 2024.10 | 오토모티브 IP 기능안전 전문가(FSE) 확보, ISO 26262 인증 추진 시작 |

| 2025.02 | 국내 주요 시스템 반도체 설계사와 TCON용 TX PHY IP 라이선싱 계약 |

| 2025.06 | UCIe 2.0 규격 인터페이스 IP 개발 성공 (국내 최초, 최대 512Gbps) |

| 2025.09 | 중국 팹리스에 8nm PCIe Gen PHY IP 공급 계약 (11억원 규모) |

| 2025.11 | 미국 AI 반도체 스타트업과 4nm UCIe·PCIe Gen 6.0 번들 IP 공급 계약 (약 30억원) |

4.사업개요

[핵심 사업]

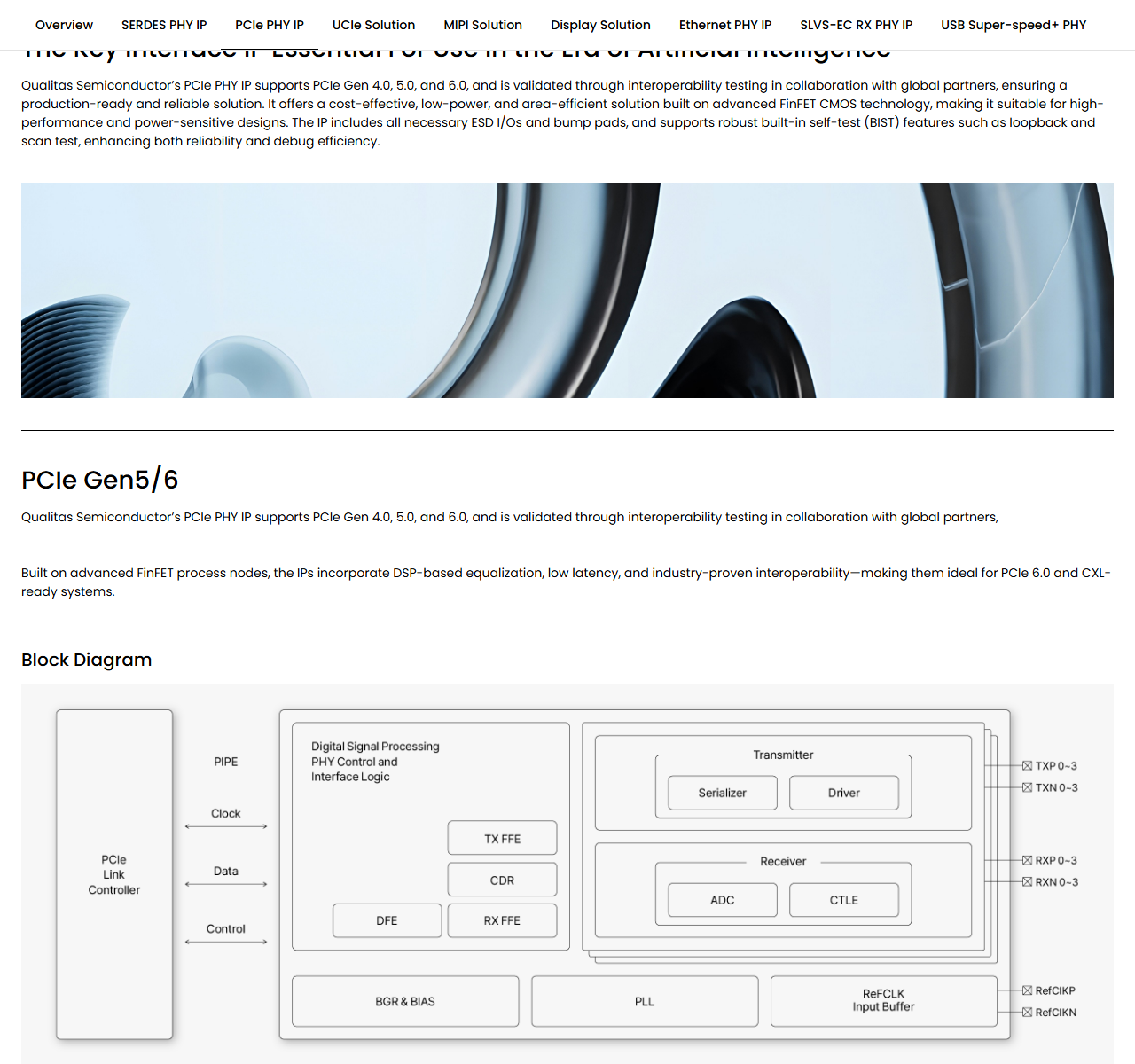

▶ 인터페이스 IP 라이선싱 : 퀄리타스반도체의 핵심 사업으로, 반도체 칩 내부의 고속 데이터 전송을 담당하는 SerDes(Serializer/Deserializer), PHY(Physical Layer), 컨트롤러 IP를 설계하여 라이선싱합니다. PCIe Gen 4.0~6.0, UCIe 2.0, MIPI CSI-2/DSI-2, eDP 등 다양한 국제표준 인터페이스 IP를 보유하고 있으며, AI 가속기, 데이터센터 서버, 스마트폰, 디스플레이 패널 등에 탑재됩니다.

▶ IP 디자인 서비스 : 고객사의 SoC 개발을 지원하는 맞춤형 설계 서비스입니다. 고객의 요구사양에 따라 인터페이스 회로를 설계하고 시뮬레이션, 실리콘 검증까지 수행하여 설계도면과 지식재산권을 제공합니다. 삼성전자 파운드리 4~8nm 공정 기반의 실리콘 프로븐(Silicon-Proven) IP를 다수 확보하고 있어, 고객사의 칩 개발 기간과 리스크를 획기적으로 줄여줍니다.

▶ 칩렛 인터페이스 솔루션 : 차세대 반도체 패키징 기술인 칩렛(Chiplet) 아키텍처에서 Die-to-Die 고속 통신을 위한 UCIe(Universal Chiplet Interconnect Express) IP 솔루션입니다. AI 가속기, HPC(고성능 컴퓨팅), 데이터센터용 SoC에서 복수의 칩렛을 하나의 패키지로 통합할 때 필수적인 인터커넥트 기술로, 엔비디아·인텔·삼성·AMD 등이 참여한 UCIe 컨소시엄 표준을 따릅니다.

[핵심 기술력 및 기술 난도]

▶ UCIe 2.0 칩렛 인터페이스 PHY IP : 칩렛 간 초고속 데이터 전송을 위한 UCIe 2.0 규격 PHY IP로, 32개 송수신 채널을 통해 최대 512Gbps(56GB/s) 전송 속도를 구현합니다. 32개 채널 전체의 패키지 전송 트레이스 폭이 약 1mm 수준으로 극히 좁아, 기존 PCIe 대비 월등한 전송 밀도를 제공합니다.

▶ 타사 대비 차별점 : UCIe IP를 실리콘 검증까지 완료한 기업은 전 세계적으로 케이던스, 시놉시스, 알파웨이브, 퀄리타스반도체 등 극소수에 불과합니다. 특히 퀄리타스는 PCIe와 UCIe를 동시에 직접 개발·공급할 수 있는 국내 유일의 IP 기업으로, PHY와 컨트롤러를 통합한 Sub-System 형태의 번들 공급이 가능합니다.

▶ 기술 난도 : UCIe는 칩렛 간 1mm 이내 초근접 거리에서 32Gbps 이상의 속도로 신호를 주고받아야 하므로, 신호 무결성(Signal Integrity)과 전력 효율을 동시에 확보해야 합니다. 스탠다드·어드밴스드 패키징 양 방식 모두 대응해야 하며, 패키지 설계·테스트 보드 설계·실리콘 검증까지 전 과정을 자체 수행할 수 있는 역량이 필요합니다.

▶ PCIe Gen 6.0 PHY IP (64GT/s) : 차세대 PCIe 6.0 표준을 지원하는 PHY IP로, 64GT/s의 전송 속도와 PAM4 시그널링 방식을 채용하여 기존 PCIe 5.0 대비 대역폭이 2배로 향상됩니다. AI 서버, HPC, 고성능 SSD 등에서 CPU/GPU와 가속기·스토리지 간 초고속 데이터 전송에 사용됩니다.

▶ 타사 대비 차별점 : 삼성전자 파운드리 4nm 공정 기반으로 실리콘 검증을 완료하여, 삼성 파운드리를 이용하는 글로벌 팹리스 고객에게 즉시 적용 가능한 실리콘 프로븐 IP를 제공합니다. 중국 팹리스의 삼성 파운드리 수요 증가와 맞물려 고객 기반이 확대 중입니다.

▶ 기술 난도 : PCIe 6.0은 PAM4(4레벨 펄스 진폭 변조) 시그널링을 도입하여 기존 NRZ(2레벨) 대비 노이즈 마진이 1/3로 줄어듭니다. 이에 따라 이퀄라이제이션, 클럭 데이터 복원(CDR), FEC(Forward Error Correction) 등 고도의 아날로그/혼합신호 설계 기술이 필수적이며, 개발 기간이 3~5년 소요됩니다.

▶ 100G급 SerDes(직렬/병렬 변환기) 설계 기술 : 112Gbps PAM4 방식의 초고속 SerDes PHY IP를 개발하여 국내 최초로 100G급 SerDes 생산기술을 확보했습니다(세계 7번째). SerDes는 반도체 칩 간 대용량 데이터를 고속으로 전송하는 핵심 인터페이스 기술로, AI 가속기와 데이터센터 네트워크 스위치에 필수적입니다.

▶ 타사 대비 차별점 : 세계 7번째로 100G급 SerDes 기술을 확보했으며, 삼성 파운드리 공정에 최적화된 SerDes IP를 제공하는 유일한 국내 업체입니다. 글로벌 대기업인 시놉시스, 케이던스, 알파웨이브 등에 이어 기술력을 인정받고 있습니다.

▶ 기술 난도 : 100G급 SerDes는 PAM4 변조 방식의 4단계 전압 레벨을 정밀하게 제어해야 하며, 고주파 신호의 노이즈, 지터(Jitter), 채널 손실 보상 등 복합적인 엔지니어링 난제를 해결해야 합니다. 아날로그 설계 전문 인력 양성에 10년 이상이 소요되어 후발주자 진입이 매우 어렵습니다.

[신규 사업]

▶ AI 가속기용 칩렛 Sub-System IP : UCIe PHY와 컨트롤러를 통합한 Sub-System 형태의 IP 패키지를 개발하여, AI 반도체 스타트업의 칩 개발 기간을 단축시키는 'Start-up Program'을 운영하고 있습니다. 미국 AI 스타트업과의 첫 번들 계약(30억원)으로 사업 모델을 검증했습니다.

▶ 오토모티브(자동차) 반도체 IP : ISO 26262 기능안전 인증(ASIL-D)을 추진하여 자율주행 및 ADAS용 반도체에 적용 가능한 인터페이스 IP 시장에 진출할 계획입니다. TUV 라인란드 코리아와 업무협약을 체결하고 기능안전 전문가(FSE)를 확보하였습니다.

▶ 글로벌 시장 직접 영업 확대 : 기존 삼성 파운드리 생태계 중심에서 벗어나 미국, 중국, 유럽 팹리스 기업에 대한 직접 영업을 강화하고 있습니다. 2025년 하반기에만 중국·미국·유럽 소재 기업과 총 51억원 규모의 IP 라이선스 계약 3건을 체결했습니다.

5. 주요 제품 매출 구성

| 사업부문 | 주요 제품/서비스 | 2022년 | 2023년 | 2024년 | |

| 반도체 IP | 매출액 | PCIe·UCIe·MIPI·eDP PHY/컨트롤러 IP 라이선스 및 설계 서비스 |

10,800 | 10,700 | 6,100 |

| 비중 | 100% | 100% | 100% | ||

| 합 계 | - | 10,800 | 10,700 | 6,100 | |

* 단위: 백만원 (별도 기준). 사업부문별 세부 매출 미공개. MIPI → eDP → PCIe·UCIe·SerDes 중심으로 매출 구성 변화 중

6-1 연간 재무

6-2 분기 재무

7. 주주 정보

| 성 명 | 관 계 | 주식의 종류 | 소유주식수 및 지분율 | 비 고 | |||

| 기 초 | 기 말 | ||||||

| 주식수 | 지분율 | 주식수 | 지분율 | ||||

| 김두호 | 본인 | 보통주 | 2,909,760 | 26.68 | 2,954,029 | 21.21 | - |

| 최광천 | 등기임원 | 보통주 | 1,426,320 | 13.08 | 1,430,945 | 10.27 | - |

| 한평수 | 등기임원 | 보통주 | 269,920 | 2.47 | 269,920 | 1.94 | - |

| 계 | 보통주 | 4,606,000 | 42.23 | 4,654,894 | 33.41 | - | |

| 성명 | 생년월일 | 직위 | 담당업무 | 주요경력 | 소유주식수 | 재직기간 | 임기만료일 |

| 김두호 | 1981.06 | 대표이사 (사내이사) |

CEO | 연세대 전기전자공학 박사 前 삼성전자 반도체사업부 책임연구원 現 퀄리타스반도체 대표이사 |

2,954,029 | 2017.02~ | 2027.03.31 |

| 한평수 | 1976.02 | 전무 (사내이사) |

CTO | 연세대 전기전자공학 박사 前 LG전자 SIC센터 책임연구원 現 퀄리타스반도체 CTO |

269,920 | 2019.01~ | 2025.03.31 |

| 최광천 | 1983.10 | 전무 (사내이사) |

AE팀장 | 연세대 전기전자공학 박사 前 삼성전자 System LSI 책임연구원 現 퀄리타스반도체 AE팀 개발팀장 |

1,430,945 | 2017.02~ | 2027.03.31 |

| 김우석 | 1973.04 | 이사 (미등기) |

MIP팀 연구위원 |

서울대 전기공학부 석사 前 온세미컨덕터 Automotive개발팀 前 아나로그디바이스 R&D센터 前 삼성전자 DDI개발 책임연구원 現 퀄리타스반도체 MIP팀 연구위원 |

- | 2018.11~ | - |

| 성창경 | 1981.03 | 상무 (미등기) |

SIP팀장 | 연세대 전기전자공학 박사 前 삼성전자 파운드리 사업부 수석연구원 現 퀄리타스반도체 SIP팀 개발팀장 |

- | 2020.06~ | - |

8. 관련 정보

9-1 관련 기사

-제목 : 퀄리타스반도체, 'UCIe 2.0 규격 인터페이스 IP' 개발 성공

-날짜 : 2025년 06월 19일

-내용 : 퀄리타스반도체가 칩렛 간 초고속 통신 표준인 UCIe 2.0 규격 PHY IP를 국내 최초로 개발 완료했습니다. 32개 송수신 채널을 통해 최대 512Gbps 전송 속도를 구현하며, 패키지 설계·테스트 보드 설계·실리콘 검증까지 자체 수행했습니다. ARM·시놉시스 등이 장악한 글로벌 IP 시장에서 국내 기업의 독자 규격 대응 성공으로 평가됩니다.

-링크 : https://www.thelec.kr/news/articleView.html?idxno=36839

9-2 관련 기사

-제목 : 퀄리타스반도체, 美 AI 반도체 스타트업과 4nm UCIe·PCIe 번들 IP 공급 계약 체결

-날짜 : 2025년 11월 21일

-내용 : 퀄리타스반도체가 미국 AI 반도체 스타트업과 약 30억원 규모의 4nm 공정 UCIe PHY·컨트롤러 및 PCIe Gen 6.0 PHY IP 공급 계약을 체결했습니다. 칩렛 인터페이스 UCIe IP의 첫 번째 라이선싱 계약이며, PHY와 컨트롤러를 통합한 Sub-System 형태로 제공하여 고객 개발 기간을 단축합니다.

-링크 : https://www.industrynews.co.kr/news/articleView.html?idxno=73646

9-3 관련 기사

-제목 : 퀄리타스반도체, 중국 팹리스에 PCIe PHY IP 공급 - 11억원 규모

-날짜 : 2025년 09월 16일

-내용 : 퀄리타스반도체가 중국 팹리스 업체와 11억원 규모의 IP 라이선스 계약을 체결했습니다. 8nm 공정 기반 PCIe Gen PHY IP로, 최근 매출액 대비 18.53%에 해당합니다. 중국 팹리스 기업들이 TSMC 대신 삼성전자 파운드리로 전환하는 추세에 맞춰 수요가 확대되고 있습니다.

-링크 : https://www.thelec.kr/news/articleView.html?idxno=40882

9-4 관련 기사

-제목 : 퀄리타스반도체, 상장 반년 만에 유상증자 - 주주들 반발

-날짜 : 2024년 05월 22일

-내용 : 2023년 10월 코스닥 상장 후 반년 만에 약 595억원 규모의 주주배정 유상증자를 결의하여 논란이 확산되었습니다. 조달 자금은 차세대 칩렛 인터페이스 UCIe PHY IP 개발에 투입할 계획이며, 최종 발행가액은 1만6,040원으로 약 415억원이 조달되었습니다. 기술성장기업 특례상장 기업에 대한 신뢰 논란이 제기되었습니다.

-링크 : https://www.sisajournal-e.com/news/articleView.html?idxno=402658

9-5 관련 기사

-제목 : 김두호 퀄리타스반도체 대표 "올 하반기 PCIe·UCIe IP 수주 본격화"

-날짜 : 2025년 07월 23일

-내용 : 김두호 대표가 PCIe 6.0과 UCIe를 양대 성장축으로 제시하며, 삼성전자 4~8nm 공정 기반 IP의 실리콘 검증 완료를 밝혔습니다. 미국·중국 시장을 중심으로 고객사 논의를 진행 중이며, 2026년 흑자전환과 640억원 매출 달성을 목표로 하고 있습니다. IP 포트폴리오를 전년 대비 2배 가량 확충했습니다.

-링크 : https://zdnet.co.kr/view/?no=20250723095501

10. 사업 검토

| 구분 | 퀄리타스반도체 (Target) | Alphawave Semi (경쟁사 1) | Cadence (경쟁사 2) |

| 회사명 | 퀄리타스반도체 | Alphawave Semi (LSE: AWE) | Cadence Design Systems (NASDAQ: CDNS) |

| 기업 성격 | 초고속 인터커넥트 IP 전문 팹리스, 삼성 파운드리 기반 PCIe·UCIe·MIPI IP 설계·라이선싱 | 캐나다 토론토 본사, 고속 연결 IP·커스텀 실리콘·칩렛 솔루션 글로벌 공급사 | 미국 산호세 본사, 글로벌 EDA·반도체 IP·시스템 분석 양대 과점 기업 |

| 시가 총액 | 약 6,965억원 | 약 24억 달러 (약 3.2조원) | 약 826억 달러 (약 112조원) |

| 2024년 매출 | 약 61억원 | 약 3.08억 달러 (약 4,200억원) | 약 46.4억 달러 (약 6.3조원) |

| 2024년 순이익 | 순손실 약 191억원 | 순손실 약 3,290만 달러 | 약 10.6억 달러 (약 1.4조원) |

| 주력 제품 | PCIe 4.0~6.0 PHY IP, UCIe 2.0 PHY/컨트롤러 IP, MIPI/eDP 디스플레이 IP, 112G SerDes | 112G/224G SerDes IP, PCIe 6.0 IP, UCIe IP, 커스텀 실리콘, I/O 칩렛 | EDA 소프트웨어(Virtuoso, Innovus), PCIe/DDR/HBM/UCIe IP, 시스템 분석 솔루션 |

| 핵심 보유 기술 | 삼성 4nm 기반 UCIe 2.0 실리콘 검증, PCIe 6.0 PAM4 PHY, MIPI 양산 프로븐 IP, 100G SerDes | 3nm 224G SerDes, 멀티 프로토콜 고속 연결, TSMC/삼성 듀얼 파운드리, 240+ IP 포트폴리오 | AI 기반 EDA 자동화, 업계 최대 IP 포트폴리오, 멀티피직스 시스템 분석, 전 공정 커버 |

| 차별화 강점 | PCIe+UCIe 동시 공급 국내 유일, 삼성 파운드리 밀착 협력, 85% 기술인력 비율, 중국 시장 접근성 | IP~커스텀 실리콘 수직 통합, TSMC OIP 5년 연속 수상, 2027년 US$1B 매출 목표 | EDA+IP 통합 생태계 락인 효과, 글로벌 모든 주요 파운드리 파트너, 시장 과점적 지위 |

| 비고 | 대상 기업 | 고속 인터커넥트 IP 직접 경쟁, 규모·포트폴리오에서 압도적 우위 | EDA+IP 복합 경쟁, 자본력·고객기반에서 압도적 차이 |

[핵심 분야별 상세 성장성 분석]

► 칩렛(Chiplet) 인터페이스 IP : AI 반도체 패키징 혁신이 만드는 신규 시장

글로벌 칩렛 시장은 2024년 약 33억 달러에서 2030년 약 190억 달러로 연평균 성장률(CAGR) 약 34%의 폭발적 성장이 전망됩니다(Yole Group). AI 가속기의 다이(die) 크기가 레티클 한계에 도달하면서 복수의 칩렛을 하나의 패키지로 통합하는 아키텍처가 표준으로 자리잡고 있으며, UCIe 표준은 엔비디아·인텔·삼성·AMD·TSMC 등 60개 이상 기업이 참여하는 국제 컨소시엄에 의해 주도되고 있습니다. 퀄리타스반도체는 UCIe 2.0 IP를 실리콘 검증까지 완료한 전 세계 극소수 기업 중 하나로, 미국 AI 스타트업과의 첫 UCIe 라이선싱 계약(30억원)을 통해 상업성을 입증했습니다. 다만 케이던스·시놉시스 등 대형 EDA 기업의 IP 사업 확장과 자본력 격차가 장기적 리스크 요인입니다.

► PCIe 6.0 / 고속 인터커넥트 IP : AI 데이터센터 대역폭 폭증이 이끄는 구조적 수요

글로벌 반도체 인터페이스 IP 시장은 2024년 약 24억 달러에서 2029년 약 54억 달러로 CAGR 약 17.6% 성장이 전망됩니다(IPnest). AI 서버 1대당 탑재되는 GPU가 8~16개로 증가하면서 CPU-GPU, GPU-GPU, GPU-스토리지 간 초고속 인터커넥트 수요가 폭발적으로 늘고 있습니다. PCIe 6.0은 Gen 5.0 대비 대역폭이 2배(64GT/s)로 향상되어 차세대 AI 서버의 필수 인터페이스로 부상하고 있으며, 퀄리타스반도체는 삼성 파운드리 4~8nm 공정 기반의 실리콘 프로븐 PCIe 4.0~6.0 IP를 확보하고 있습니다. 특히 중국 팹리스 기업의 삼성 파운드리 이용 확대와 맞물려 중국 시장에서 빠른 고객 기반 확장이 기대됩니다.

► 디스플레이 인터페이스 IP : 고해상도·고주사율 디스플레이 확산의 수혜

글로벌 디스플레이 드라이버 IC(DDI) 시장은 2024년 약 82억 달러에서 2030년 약 112억 달러로 CAGR 약 5.3% 성장이 예상되며(Market Research Future), 특히 OLED 확산·4K/8K 고해상도·고주사율(120~240Hz) 트렌드가 디스플레이 인터페이스 IP 수요를 견인하고 있습니다. 퀄리타스반도체는 MIPI CSI-2/DSI-2, eDP v1.5a 등 양산 프로븐 IP를 보유하고 있으며, 글로벌 톱티어 IT 기업의 디스플레이 제품에 이미 탑재되고 있습니다. 중화권 SoC 업체에 DSI-2 컨트롤러를 공급하며 포트폴리오를 확장했으며, 이 분야는 퀄리타스의 안정적 매출 기반이자 캐시카우 역할을 합니다.

[향후 극복 필요한 기술장벽]

► 224G PAM4 SerDes 기술 격차 해소 : 차세대 데이터센터 표준 속도 달성의 난제

현재 퀄리타스반도체가 확보한 100G급(112Gbps) SerDes 기술은 현세대 표준이지만, 업계는 이미 224Gbps(200G급) PAM4 SerDes로 전환하고 있습니다. Alphawave, 시놉시스, 케이던스 등 글로벌 선두업체들은 이미 224G SerDes IP를 개발 완료하거나 실리콘 검증 단계에 있습니다. 224G는 112G 대비 2배의 데이터율을 동일 채널에서 구현해야 하므로 신호 대 잡음비(SNR) 마진이 극도로 줄어들어 DSP(디지털 신호 처리) 기술이 필수적이며, 전력 소비도 크게 증가합니다. 이 기술을 적시에 확보하지 못하면 800G/1.6T 이더넷 기반 AI 데이터센터 시장에서의 경쟁력이 약화될 수 있습니다.

► 삼성 파운드리 단일 의존도 탈피 : TSMC 등 멀티 파운드리 IP 지원 필요성

퀄리타스반도체의 IP는 삼성 파운드리 공정(4nm~14nm)에 최적화되어 있으나, 글로벌 팹리스 시장에서 TSMC의 점유율이 약 60%를 차지합니다. 미국·유럽의 대부분 팹리스 고객은 TSMC 공정을 사용하므로, 삼성 파운드리 전용 IP만으로는 잠재 고객의 약 60%에 접근할 수 없는 구조적 한계가 있습니다. TSMC 공정용 IP를 개발하려면 별도의 PDK(Process Design Kit) 확보, 테스트칩 제작, 실리콘 검증 등 수백억원의 추가 투자와 2~3년의 개발 기간이 필요합니다. 삼성 파운드리와의 핵심 협력 관계를 유지하면서도 고객 기반을 넓히는 전략적 균형이 장기 성장의 핵심 과제입니다.

► 적자 탈출 및 수익성 확보 : IPO 이후 지속되는 적자의 구조적 해소 과제

퀄리타스반도체는 2022년 매출 108억원/영업손실 37억원, 2023년 매출 107억원/순손실 81억원, 2024년 매출 61억원/순손실 191억원으로 매출이 역성장하고 적자가 확대되는 추세입니다. IPO 당시 제시한 2024년 흑자전환 전망(순이익 28억원)과 실제 실적 간 큰 괴리가 발생했으며, 2025년 3분기까지도 누적 순손실 153억원을 기록하고 있습니다. 김두호 대표는 2026년 흑자전환을 목표로 제시했으나, 유상증자로 조달한 415억원이 소진되기 전에 매출 성장과 수익성 개선을 달성하지 못하면 추가 자금 조달이 불가피하여 기존 주주 가치 희석 리스크가 존재합니다.

'종목탐색 > AI, 반도체' 카테고리의 다른 글

| [종목 탐색] 버티브홀딩스 (Vertiv Holdings) (0) | 2026.03.27 |

|---|---|

| [종목 탐색] 필옵틱스 (0) | 2026.03.13 |

| [종목 탐색] 이스트소프트 (0) | 2026.03.13 |

| [종목 탐색] 이수페타시스 (0) | 2026.03.13 |

| [종목 탐색] 오픈엣지테크놀로지 (0) | 2026.03.13 |